MSc thesis project proposal

Digital processing for large pixel array 3D-TOF systems

Project outside the university

Silicon Integrated, EindhovenAbout the Company:

Silicon Integrated Co., Ltd is a high-tech startup company focusing on high-performance mixed-signal IC design. It was founded in January 2016 in Wuhan and it has R&D centers in Europe, Shenzhen and Shanghai. Silicon Integrated has two main product lines: 3D image sensors and smart audio amplifiers. The smart audio amplifier wins over the business by excellent product differentiation, with high-quality performance and competitive price. The business value is fully recognized by the tier-one smartphone manufacturers in China.

Business Line Description:

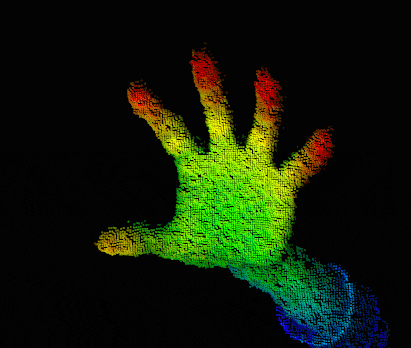

The 3D image sensor product features a time-of-flight (ToF) function, by using state-of-art back-side illuminated (BSI) and near infrared (NIR) enhancement technology, which enables high precision, small pixel , high resolution and low power features in one fully integrated chip. This 3D image sensor can be widely applied in artificial intelligence, facial recognition, self-driving cars, 3D modelling, fast movement capture, and machine vision. The ToF sensor and 3D imaging system are expected to create a very promising market prospect being widely used in mobile, surveillance and automotive industries.

Project Description:

For SPAD sensors, a major benefit is the potential for designing large pixel arrays. However, a large pixel array implies massively parallel time-resolved measurements resulting in a large volume of data. For example, for a 200 x 160 pixel array with 1 us measurement periods and 10 bit TDC, there are 320 GBits of data generated per second. Transferring this huge amount of data is impractical for a number of reasons, including high power consumption and high number of data pins. As a result, a power/area efficient algorithm is needed for on chip data processing.

Assignment

The assignment is to closely work with senior engineers to develop new data processing algorithms for advanced 3D-TOF systems with the following properties:

- able to process a 200 x 160 pixel array with 30 fps

- power consumption should be state-of-the-art

- memory usage should be as small as possible

- the algorithm should be implemented with RTL and mapped to FPGA

- the FPGA should be connected to a real SPAD/TDC to evaluate the performance of the algorithm

Requirements

- Familiar with RTL design language, such as Verilog, VHDL

- Experience with FPGA design flow

- Experience in ASIC/SoC design and methodologies is a plus

- Knowledge of signal processing for TOF systems is a plus

- Strong communications, documentation, and presentation skills

- Highly self-motivated and enjoying solving difficult challenges

- Currently enrolled in a Master's degree program in Electrical Engineering, Computer Engineering, or related fields

Contact

prof.dr.ir. Geert Leus

Signal Processing Systems Group

Department of Microelectronics

Last modified: 2023-11-03