MSc thesis project proposal

High-speed (RF) chopping (NXP)

Project outside the university

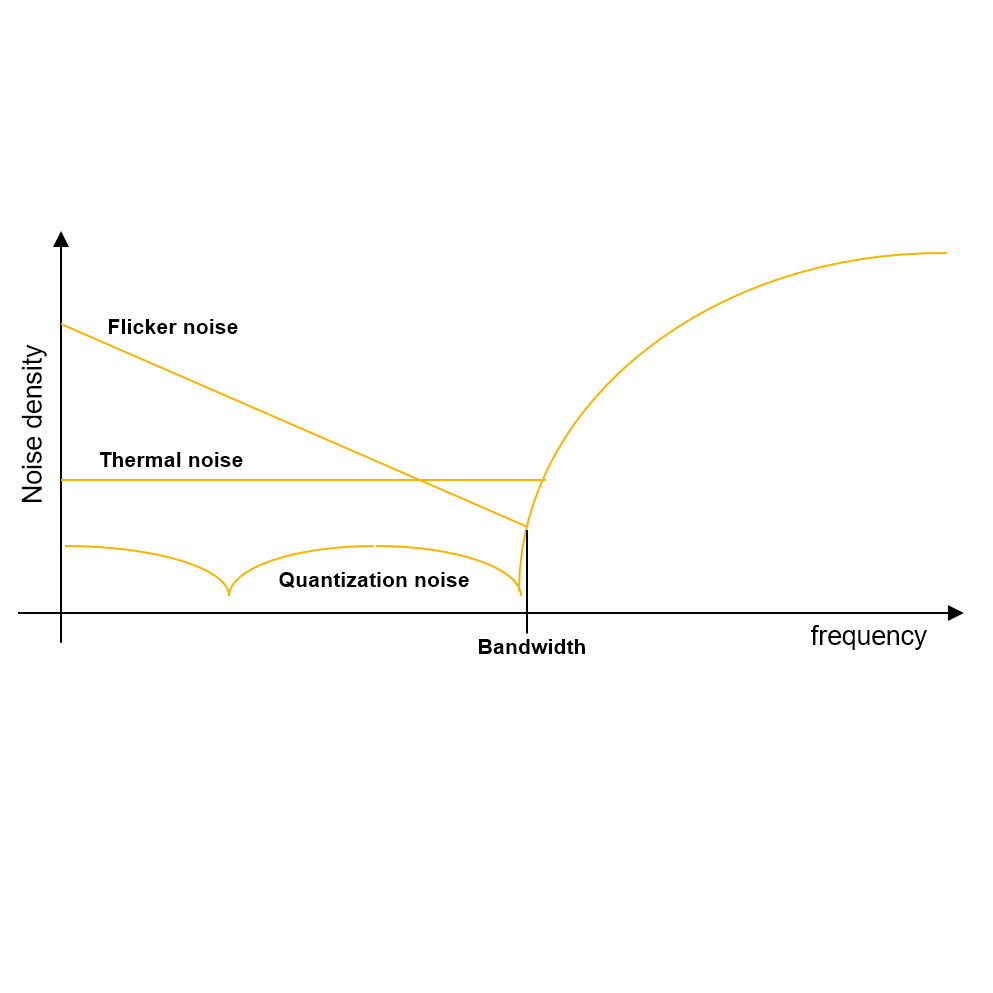

NXP SemiconductorsFuture automotive car radar applications require a data converter with a bandwidth larger than 40MHz and a very low 1/f noise corner frequency. High-speed sigma-delta modulators sampled at several GHz can achieve such a wide bandwidth. However, 1/f noise introduced by the amplifiers of the loop filter of the modulator limits its noise performance. In this thesis project, we will investigate 1/f noise reduction techniques of sigma-delta modulators sampled at GHz frequencies. This thesis will be a part of the running PhD project entitled “RF Chopping”. The project will start with a feasibility study where several techniques will be identified. The most promising technique(s) will be further developed during the MSc thesis project.

In this master thesis project you will do/learn:

- In depth study of ADC (or DAC) architecture

- Design of analog and mixed-signal circuits in 28nm CMOS

- Circuit simulations with Spectre (or other simulator)

- Layout design of circuits and simulation of extracted layout

- Build understanding of impact of process imperfections and parasitic artifacts on performance

Assignment

Overview of the project planning (depending on the progress of the student)

- Literature review of chopping techniques of sigma-delta modulators.

- System level study of the proposed architecture in Matlab/Cadence.

- Circuit and layout implementation.

- Tape-out of the IC followed by measurement.

- Process node: 28nm HPCP.

- Target tape-out date: Sep 2022.

A stipend is provided.

Requirements

- Good knowledge of analog and mixed circuit design.

- Good understanding of Data Converters.

- Familiarity with Matlab and Cadence.

- You will be collaborating with researchers from NXP Semiconductors so good communication and presentation skills are essential.

Contact

dr.ir. Muhammed Bolatkale

Electronic Instrumentation Group

Department of Microelectronics

Last modified: 2024-02-07