# A new current mode synthesis method for dynamic translinear filters and its application in hearing aids

D.Masmoudi\*, W.Serdijn\*\*, J.Mulder\*\*, A.v.d.Woerd\*\*, J.Tomas\* and J.P.Dom\*

\*:Bordeaux 1 University, I.X.L. Laboratory- UMR 5818, 351 cours de

la libération, 33405 Talence, France

\*\*:Delft University of technology, Faculty of electrical engineering,

Mekelweg 4, 2628 CD Delft, The Netherlands.

e-mail: masmoudi@ixl.u-bordeaux.fr; phone: (33)556845280; fax: (33)556371545

#### Abstract

A new current mode synthesis method for dynamic translinear filters is proposed. As a design example, we have considered an ultra-low power second order filter working in audio frequency range, for hearing aids application, and using subthreshold MOS devices. It has a nominal supply voltage of 1.2 Volt and works down to 1Volt. The total power consumption is about 5  $\mu W$ . The filter cut-off frequency and its Q factor can be tuned respectively from 600Hz to 13kHz and from 0.6 to 1.1. Mismatch problems are investigated on the circuit level and an on-chip compensation method is proposed.

#### 1. Introduction

The use of ultra-low power and low voltage techniques in hearing aids allows miniaturization of the supply systems and increases their autonomy. However, lowering the supply voltage leads to limitations in voltage swings. Using current mode operations in a filter design doesn't exclude the voltage importance as an information carrying quantity, since the most important function in an integrated filter i.e the integration is effectuated by a capacitance that integrates a current into a voltage. This dual importance of voltage and current in filter processing can be solved in a low voltage environment by operating in a current mode and introducing a non-linear transfer between both quantities so that the voltage swings are much lower than the current swings. Such techniques can make use of the expanding law between voltage and current, present either in the bipolar device or in the subthreshold MOS device and constitute a more general class of dynamic translinear filters or E.S.S. filters. This class was first introduced by Adams [1], and generalized to filters of arbitrary orders by Frey [2]. Recently, it has gained much interest in audio filter applications [3] [4] owing to its excellent tunability, its interest for ultra-low power applications since no resistors are necessary and to the fact that it can be designed temperature independent.

Dynamic translinear circuits can be described using voltage as well as current quantities. However, a completely current mode synthesis method of T.L filters fits better with the simplicity of their current mode analysis [5], and can potentially make use of the static translinear circuit theory [6].

Moreover, subthreshold MOS translinear circuits have some fundamental advantages over bipolar translinear circuits. First,

they don't suffer from the finite current gain like bipolar devices and they have a low saturated voltage which is more convenient in a low power and low voltage design. Second, unlike the bipolar device, the MOS is a four terminal device, which gives in subthreshold an extra exponential dependency of the drain current and therefore more possible configurations over bipolar realizations. However, one of the limitations of the MOS operating in weak inversion is the current mismatch between identically designed devices due to the process variations [9]. This poor control of the current match causes a number of undesirable effects in the circuit level. Traditionally, several layout techniques such as making devices large and placing devices close to each other have been proposed for improving the transistors matching. However, it is more accurate and more area efficient to solve the problem on circuit level notably if an on-chip mismatch compensation method can be proposed.

In this paper, we present a general completely current mode synthesis method for dynamic translinear filters. Then a design example employing subthreshold MOS is proposed followed by an investigation of the mismatch effects on the circuit level. In section II, a mathematical formulation of the proposed method is exposed. In section III, a second order controllable filter design for audio applications is presented. Section IV is subject of an analysis of the mismatch effects on the circuit level, focusing on a robust on-chip design method to overcome mismatch problems. The full-custom realization and the measurement results of the corresponding design are presented in section V. Finally, the conclusion is presented in section VI.

# 2. Overview of a completely current-mode synthesis method for dynamic translinear filters

#### 2.1. Mathematical formulation

The synthesis method starts with a variable state representation of the filter differential equation. Such representation has the general form given by

$$\dot{X} = AX + BU$$

(1)

$Y = EX + DU$  (2)

Where the dot indicates time differentiation,  $X = (x_1, x_2, ..., x_n)$

Where the dot indicates time differentiation, X=(x1,x2,...,xn) is a vector of state variables and U and Y are respectively the input and the output currents. Time derivation can be

accomplished by the introduction of capacitance currents as illustrated in the general key substructure of dynamic translinear filters represented in fig.1. A general relation describing the exponential device is given by

$$I_{Ci} = Ie^{\frac{V_i}{\alpha V_T}}$$

(3)

Where I and  $\alpha$  are constants depending on the exponential device and  $V_T$  is the thermal voltage kT/q. Vconst is a constant voltage which is generally introduced by a buffer of the capacitance voltage avoiding so any interaction between the different blocks in the design. The capacitance current is found by applying the constitutive relation of the capacitance comprising the derivative of the capacitor node voltage which can be deduced from eqn.3 as follows

Icapi =

$$\alpha CV_T \frac{I_{Ci}}{I_{Ci}}$$

(4)

Eqn. 4 shows that the derivative of a current can be deduced from the product of two currents. The latter can be implemented by means of a static translinear multiplier. This invites a new way of thinking in filter design and signal processors. The basic cell is no longer a linear one. Instead, It can be rather a multiplier or another cell dealing with current multiplication/division.

Now, taking as state variables the currents  $I_{\text{Ci}}$ , we get for eqns.1 and 2

Icapi.

$$I_{Ci} = \sum_{i=1}^{n} I_{i,j} I_{Cj} + J_{i} U_{i}$$

(5)

$$Y_{i} = EiI_{Ci} + DiU_{i}$$

(6)

for i = 1, ..., n

where

$$I_{i,j} = \alpha Ci A_{i,j} V_{T}$$

(7)

and

$$J_i = Bi\alpha CiV_T$$

(8)

Eqns.7 and 8 reveal the possibility of tuning the A state space matrix elements and those of the B state space vector respectively by adjusting the current sources  $I_{i,j}$  and  $J_i$ . Such simplicity in tuning the design characteristics is a fundamental advantage of dynamic translinear filters. Moreover, by using PTAT current sources, temperature independent design characteristics can be achieved.

### 2.2. Choice of the exponential device in a subthreshold environment

In a saturated subthreshold MOS transistor, the drain current has two exponential dependencies, the first is with respect to its gate to substrate voltage with a process dependent slope factor and the second is relative to its back-gate to source voltage which is almost process independent. A simple model for the drain current of a MOS transistor in saturation is given by

$$I_{DS} = Ioe^{\frac{V_{GB}}{nV_T}} e^{-\frac{V_{SB}}{V_T}}$$

(9)

Where Io is the zero bias current,  $V_{GB}$  and  $V_{BS}$  are respectively the gate-bulk and source-bulk voltages and n is the subthreshold slope factor.

It follows from the above relation that different topologies are possible for the basic exponential device, they are presented in fig.2. In fig.2.a and fig.2.b, the bulk to source junction can be biased slightly forward causing some leakage current. For high

current level, the bulk voltage can increase in a way that the leakage current is no more negligible relative to the drain current. This leads to a practical exponential range limitation of the drain current estimated to two decades [7]. In fig.2.c and fig.2.a, the exponential relation has a slope depending on the MOS subthreshold slope factor which is a function of the applied voltage Vi. Finally, the configuration in fig.2.d is free from the above drawbacks by having grounded bulks and an exponential relation which is independent of the subthreshold slope factor and given by

$$I_{Ci} = Iexp\left(\frac{V_i}{V_T}\right) \tag{10}$$

#### 2.3. Implementation of the voltage buffer

To minimize the interaction between the different blocks and the capacitors in the circuit, voltage buffers are introduced. Consider the implementation of the voltage buffer shown in fig.3.a. The variations of the output voltage for this implementation are given by

$$\dot{\text{Vout}} = \frac{\dot{\text{Vin}}}{n_f} - \frac{\dot{n_f}}{n_f^2} \text{Vin}$$

(11)

Where  $n_f$  is the sub-threshold slope factor of the transistor Mf. For each particular operation of the filter, the output voltage variations are such that  $n_f$  can be considered constant. However when tuning the cut-off frequency of the filter and its Q factor, this assumption is no longer valid. To solve the resultant non-linearity, a balanced configuration based on an up-down compensation is used. The latter is represented in fig. 3.b.

### 3. A design example: a tunable secondorder low-pass filter for hearing aids

The above synthesis method is applied to the design of a second-order low-pass filter for audio applications. By using the state space description defined by

$$A = \begin{bmatrix} -\omega_c / Q & \omega_c \\ -\omega_c & 0 \end{bmatrix}, \quad B = \begin{bmatrix} 0 \\ \omega_c \end{bmatrix}, \quad E = \begin{bmatrix} 1 & 0 \end{bmatrix}, \quad D = 0 \quad (12)$$

, where  $\omega_c{=}2\pi f_c,$  and  $f_c$  is the cut-off frequency of the filter, we thus get to implement the following equations

$$Icap1.I_{C1} = -IQ.I_{C1} + I.I_{C2}$$

(13.a)

$$Icap2.I_{C2} = -I.I_{C1} + I.I_{in}$$

(13.b)

$$Iout = I_{C1} (13.c)$$

The relation between the cut-off frequency and the current source I is given by

$$f_{\rm C} = \frac{I}{2\pi {\rm CV_T}} \tag{14}$$

In order to implement a multiplication/division of currents, an up-down translinear topology is the most compatible strategy with a low voltage environment. Thus, we make use in our design of the static translinear loops presented in fig.4. By considering successively the loops M2-M5-...-M9, M1-M4-M6-M7 and M2-M3-M8-M9, we get easily the following relations between the different currents

$$I_2.I_{C2} = 1.I_{C1}$$

(15.a)

$$I.I_{in} = I_1.I_{C2}$$

(15.b)

$$I_2 . I_3 = I^2$$

(15.c)

where  $I_1$ ,  $I_2$  and  $I_3$  are respectively the drain currents of transistors  $M_1$ ,  $M_2$  and  $M_3$ . Thus eqns.13 come down to the following nodal equations

$$Icap1 = -IQ + I_3 \tag{16.a}$$

$$Icap2 = -I_2 + I_1 \tag{16.b}$$

$$Iout = I_{C1}$$

(16.c)

Moreover, in some nodes such us nodes A and B, the bias voltage level should allow the flow of the needed current sink at these nodes, i.e. by having values above the saturated drain source voltage of a MOS transistor, estimated to few V<sub>T</sub> (for example 150mV). By connecting node C to ground, fulfilling this condition leads to a limitation in the upper signal value, especially for high control currents. Therefore, in order to give a larger room to nodes A and B and allow variations of the input signal over an extended range, node C should be connected to a bias voltage of few V<sub>T</sub>. A simple way of generating such a source internally, which costs only the addition of small transistors, is to use a self-cascode [8] in the input and the output levels as represented in the complete design schematic shown in fig.5. By writing the drain currents of transistors M4,  $M_5$ ,  $M_4$ ' and  $M_5$ ', and assuming that  $M_4$ ' and  $M_5$ ' are at the edge of saturation, we get easily the following expression for the

$$V_{C} = V_{T} Ln \left( 1 + \frac{\beta_{1}}{\beta_{2}} \right) \tag{17}$$

where  $\beta_1$  and  $\beta_2$  are respectively the transfer parameter  $\beta = \mu CoxW/L$  of transistors  $(M_4,M_5)$  and  $(M_4',M_5')$ . The generated voltage is then first order independent of the current signal. We also notice from this expression that  $M_4$ ' and  $M_5$ ' should be as narrow as possible in order to get a sufficient value of  $V_C$ , thus  $V_C$  is practically modulated by narrow channel effects.

The cut-off frequency of the filter can be tuned linearly by varying the control current I according to the relation in eqn.14 where the capacitance value C is chosen to be of 100 pF. Moreover, the Q factor, defined as the ratio of the control current I to the current IQ, can be also tuned by adjusting IQ. The nominal supply voltage of the design is equal to 1.2 V.

#### 4. Mismatch investigation

#### 4.1. Mismatch analysis

Mismatch problems concern all the on-chip devices, but are more significantly affecting transistors in the signal path, which we will consider in our analysis.

A mismatch between two MOS devices can be modeled by a series voltage connected between the gates of both transistors as well as between their back-gates [9] [10]. Applying the latter result to our design, the corresponding voltage sources are appended to the circuit represented in fig.5. However, it is worth noting that the mismatch between the up and down PMOS transistors of the followers comes down to a shift in their transfer gain, which is equivalent to a deviation in the corresponding capacitance value. The analysis of the whole design leads therefore to the following transfer function

$$H(s) = \frac{k_4}{\frac{k_3}{k_2} + \frac{1}{Q\omega_2 k_2 k_1} s + \frac{1}{k_1 k_2 \omega_1 \omega_2} s^2}$$

(18)

where

$$k_i = \exp \frac{(n-1)}{nV_T} \left(vb_i + vb_i^*\right)$$

for  $i = 1,2$  (19.a)

$$k_i = \exp{\frac{(n-1)}{nV_T}} (vb_i)$$

for  $i = 3,4$  (19.b)

$$Q = \frac{I}{IQ}$$

(19.c)

and

$$\omega_{1,2} = \frac{I}{C_{1,2}V_T}$$

(19.d)

The new cut-off frequency of the filter and its resonance factor are thus respectively given by

$$f_c^* = f_c \frac{\sqrt{C_1 C_2}}{C} \sqrt{k_1 k_3}$$

(20.a)

$$Q^* = Q\sqrt{k_1 k_3} \sqrt{\frac{C_2}{C_1}}$$

(20.b)

The remaining mismatch effect is a shift in the pass-band response which is deviated from a unity value to a new one given by eqn.21. Since the input signal is superimposed on a d.c. current, an offset current will appear at the output.

$$A = \frac{k_2 k_4}{k_3} \tag{21}$$

#### 4.2. Mismatch compensation

According to eqns.19, a deviation from the cut-off frequency can be recovered by adjusting the control current I. Similarly, a deviation from the desired filter factor can be surmounted by adjusting the current source IQ.

Finally, a compensation of the shift in the pass band response can be achieved by an on-chip offset cancellation. We can make use, for this purpose, of a negative feed-back, acting on both transistors P1 and P2 (see fig.5) back-gates so that the parameter k2, and then the pass-band response are adjusted (since we are using an N-well technology, the action on k3 and k4 is not possible). The schematic diagram of this compensation is represented in fig.6. The grounded capacitor C3 integrates a copy of the output current resulting in a voltage which will be transformed by D1 and D2 into a current that will be integrated by the capacitor C<sub>4</sub>. Due to the non-linear characteristics of the diode, a large offset will be reduced very fast because of the corresponding low dynamic resistance of the diode. Further, if there is almost no offset, the latter becomes very large so that no distortion of the design transfer function is observed. The backgate of the PMOS transistor P2 is connected to a voltage source, slightly below V<sub>DD</sub>, which gives a certain room for the feedback action across the capacitor C4. This voltage is generated using a self-cascode based on the same principle used for the generation of the voltage V<sub>C</sub>, but employing a d.c. current source IB. The overall matching of the filter relies now on the accuracy of the output current copy. Therefore, we use, only at this level, special layout techniques to match the output and the sensing transistors. The value of the capacitance C3 and C4, needed for the correct operations of the offset compensation, are respectively 200 pF and 20 pF.

## 5. Full-custom implementation and measurement results

The second order controllable filter is implemented in the  $1.6\mu m$  CMOS process of the Delft Institute for Microelectronics

and Submicron Technology (DIMES). A microphotograph of the design full custom realization is shown in fig.7. Its total area is about 0.2 mm² without including the bias block. All the design measurements are effectuated at a room temperature of 298K (27°C). the cut-off frequency of the filter can be tuned from 600 Hz to 13 kHz. Further, the Q factor can be tuned from 0.6 to 1.1. Correct operations of the filter can be maintained down to a supply voltage of 1V.

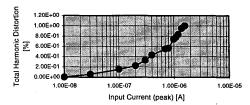

The d.c. current ensuring correct class A operations of the filter is fixed to 1.6  $\mu$ A. The total power consumption is approximately 5 $\mu$ A. The THD measured at 1 kHz versus the input current peak value, for I=210nA (fc=13kHz) and IQ=300nA, is presented in fig.8. These measurements show that the filter has a good linearity. The corresponding referred noise floor current is 1.4nA<sub>rms</sub>. The resultant D.R. is evaluated to 58 dB. Further, the THD of the filter remains below 2% over the tuning range. The performance characteristics of the filter are summarized in Tab.1.

#### Conclusion

We have proposed a completely current mode state space synthesis method for dynamic translinear filters that doesn't need high computational efforts. As an application, we have looked at ultra-low power design working in audio frequency range and using subthreshold MOS devices. Mismatch errors were investigated in the circuit level and an on-chip mismatch compensation method was proposed.

#### References

- R.W. Adams, 'Filtering in the log domain',63 rd Convention A.E.S., L A, preprint 1470, May 1979.

- [2] D.R.Frey, 'Exponential state space filters: A generic current mode design strategy', IEEE transactions on circuits and systems-I: fundamental theory and applications, vol 43,no 1,pp 34-43, jan 1996.

- [3] W.A.Serdijn, M.Broest, J.Mulder, A.C Woerd and A. H.M. Roermund, 'A low voltage ultra-low power current companding integrator for audio filter applications' IEEE Journ of solid state cir. April 1997.

- [4] W.A.Serdijn, M.H.L.Kouwenhoven, J.Mulder and A.H.M. van Roermund, 'The design of high-dynamic-range fully integratable translinear filters', Analog Integrated Circuits and Signal Processing (Kluwer), accepted for publication.

- [5] J.Mulder, A.C.v.d.Woerd, W.A. Serdijn, and A.H.M.v. Roermund, General current-mode analysis method of translinear filters, IEEE Transaction on circuits and Systems.-I, vol. 44, pp.193-197,1997.

- [6] E.Seevink,' Analysis and synthesis of translinear integrated circuits' Elseiver, Amesterdam, 1988.

- [7] J.Mulder, A.C.v.d.Woerd, W.A. Serdijn, and A.H.M.v. Roermund,' Application of the back-gate in MOS weak inversion translinear circuits,' IEEE Transaction on circuits and systems.-I, vol. 44,pp.193-197,1997.

- [8] E.Vittoz,' The fundamentals of Analog Micropower Design,'. In Tutorial 7 at ESSCIRC'96, September 1996,pp.365-372.

- [9] M.J.Chen, J.S. Ho and T.H. Huang, Dependence of current match on back-gate bias in weakly inverted MOS transistors and its modeling, IEEE Journal of solid-state circuits, vol.31, No.2, February 1996, pp.259-262.

- [10]T.H.Huang and M.J.Chen, 'Empirical modeling for gatecontrolled collector current of lateral bipolar transistors in

an n-MOSFET structure,' Solid-state Electronics, Vol.38, No.1, pp.115-119, Jan 1995.

#### Figures and captions

Figure 1: General key substructure in dynamic translinear circuits

Figure 2: Possible topologies of the basic exponential device

Figure 3: Voltage buffer (a) simple implementation (b) balanced one

Figure 4: Basic static translinear loops in the design

Figure 6: Schematic diagram of the complete design

Figure 7: A microphotograph of the design full-custom realization

Figure 8: Measured Total Harmonic Distortion [%]

| Technology     | 1.6µm CMOS process     |

|----------------|------------------------|

| Active area    | 0.2 mm <sup>2</sup>    |

| Supply voltage | 1.6V-1V (nominal=1.2V) |

| Tuning range   | 600-13kHz              |

| Tuning current | 9.1nA-210nA            |

| Q factor       | 0.6-1.1                |

| Dynamic range  | 57 dB (THD<2%)         |

Tab.1. Performance characteristics of the filter