ET4351 Digital VLSI Systems on Chip

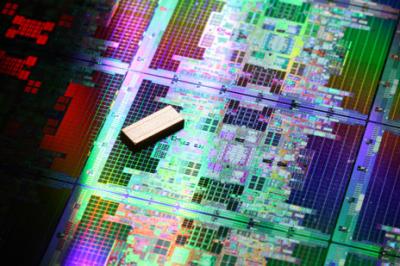

Today’s large-scale digital integrated circuits and systems-on-a-chip, such as modern general processing units (GPUs), can >50 billion transistors. Two things were instrumental in enabling this massive scalability: electronic design automation (EDA) tools and intellectual property (IP) blocks allowing for hierarchical design.

In this course, you will learn how to use such EDA tools and IP blocks to go from the register-transfer level (RTL) description of your digital design to a final layout that is clean for tapeout and meets your specifications. To do so, you will also learn about power/performance/area tradeoff optimization, hardware-algorithm co-design, and memory hierarchy.

These tools and concepts will be practiced and applied in a project, in which you will explore and apply your own design choices to meet a well-defined design target in a digital system-on-chip.

Study Goals

After successful completion of the course, you will be able to:

LO1. Design modern digital systems-on-a-chip with automated synthesis and place-and-route tools by

- identifying the key design targets and tradeoffs,

- selecting a proper IP to meet design targets,

- translating the design constraints and tradeoffs to tool commands,

- applying the tools to meet design targets.

LO2. Optimize, in a rigorous and creative manner, the power/performance/area tradeoff associated with a given application use case.

LO3. Link algorithmic requirements to hardware constraints.

LO4. Extract the key performance metrics of a digital design by

- verifying that simulation results can be trusted and that the design is clean for tapeout,

- communicating these results effectively and rigorously,

- discussing their implications within a broader societal context.

Teachers

dr. Charlotte Frenkel (EI)

Digital IC design, neuromorphic engineering and spiking neural networks, neuroscience-inspired machine learning, hardware-algorithm co-design.

Last modified: 2023-11-04